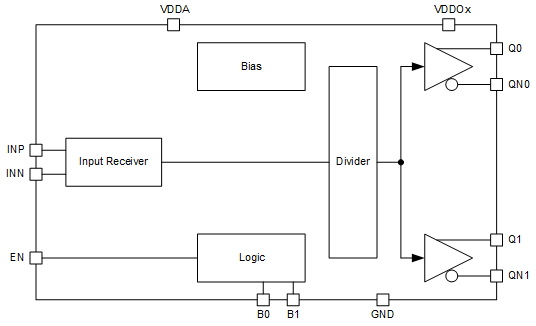

CF112P Description

The CF112P is an extremely low additive jitter 1:2 LVPECL clock fanout and divider. Its sensitive differential input receiver accepts low amplitude sinewave, CMOS, LVPECL, LVDS, CML, and HCSL signals to perform LVPECL output logic level translation, signal fanout, and configurable frequency division (or passthrough) up to 1000MHz. The CF112P is designed to meet extremely low additive jitter and skew requirements operating in an extended temperature range. The divide functionality (or passthrough) is configured with static voltages to external control pins.

Block Diagram

Your Content Goes Here

Features

- Input signal sensitivity down to 30mVpp

- Input/output signal frequency up to 1000MHz

- Additive Jitter <20fs @ 1GHz, <40fs @ 156MHz

- 30ps output to output skew

- Configurable output divider

- Extended Temp Range: -55°C to 125°C

Applications

- 5G/6G clock distribution

- Low jitter clock trees

- Logic translation & signal restoration

- Wired & Wireless communications

- Microprocessor clock distribution

- High speed ADC, DAC clock driver

Order Numbers

| Order Number | Package | Quantity / Form | RoHS | MSL Rating | Leadframe |

|---|---|---|---|---|---|

| CF112P-T1 | 16L TSLP QFN | 123 / Tube | Yes | 1 | NiPdAu |

| CF112P-R1 | 16L TSLP QFN | 1000 / 7" Reel | Yes | 1 | NiPdAu |